## Digital Circuits ECS 371

### Dr. Prapun Suksompong prapun@siit.tu.ac.th Lecture 10

**ECS371.PRAPUN.COM**

Office Hours: BKD 3601-7 Monday 9:00-10:30, 1:30-3:30 Tuesday 10:30-11:30

## Announcement

- HW4 posted on the course web site

- Chapter 5: 4(b,c,e), 20a, 22a, 56

- Write down all the steps that you have done to obtain your answers.

- Due date: July 16, 2009 (Thursday)

## **Combinational Logic**

- We studied the **theoretical** principles used in combinational logic design.

- We will build on that foundation and describe many of the devices, structures, and methods used by engineers to solve **practical** digital design problems.

- A complex circuit or system is conceived as a collection of smaller subsystems, each of which has a much simpler description.

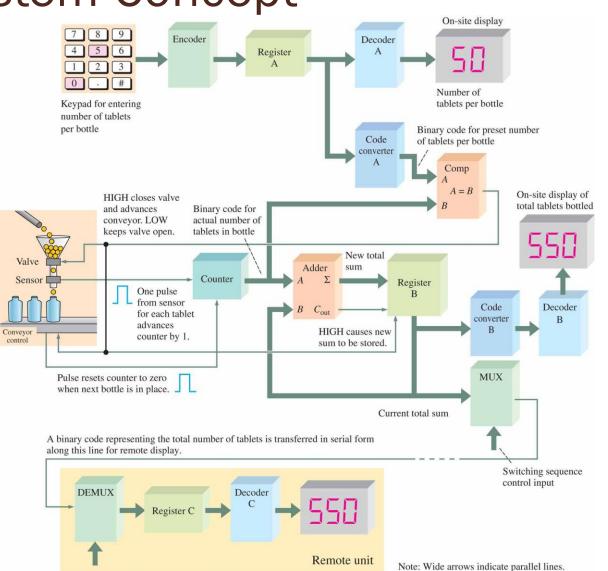

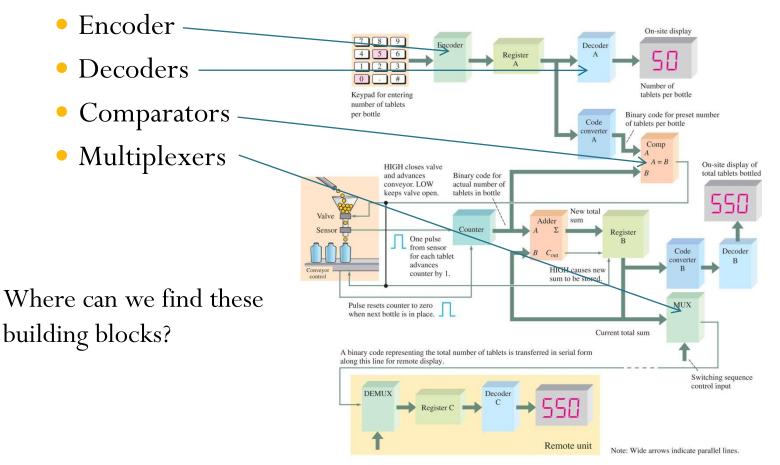

## **Digital System Concept**

A digital system

is an arrangement of the individual logic functions connected to perform a specified operation or produce a defined output.

## **Combinational Building Blocks**

• There are several straightforward structures that turn up quite regularly as building blocks in larger systems.

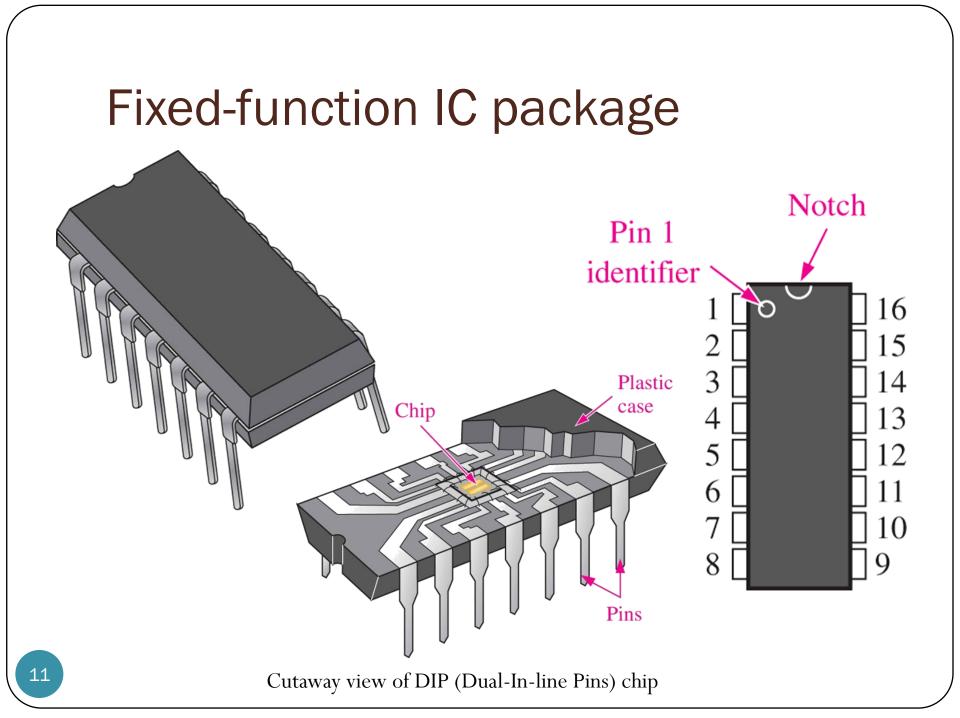

## Fixed-function IC

- An integrated circuit (IC) is an electronic circuit that is constructed entirely on a single small chip of silicon.

- Two broad categories of digital ICs.

- 1. Fixed-function logic

- 2. Programmable logic

- In **fixed-function logic**, the logic functions are set by the manufacturer and cannot be changed.

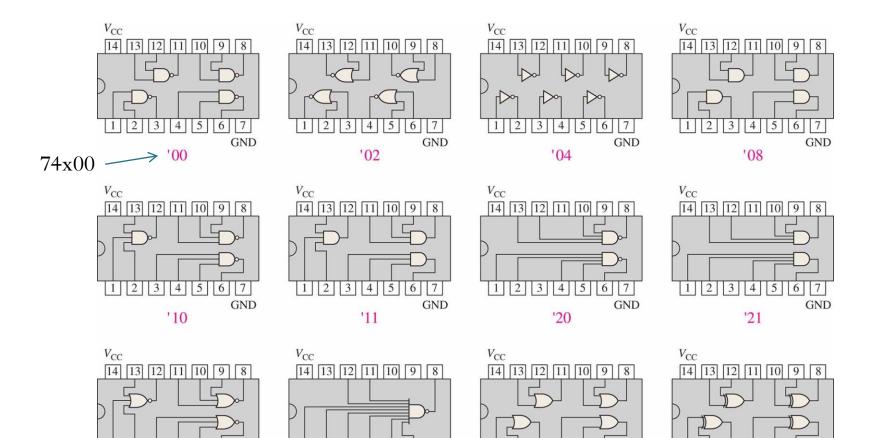

## **Complexity Classifications**

Fixed-function digital lCs are classified according to their complexity.

- Small-scale integration (SSI)

- up to ten equivalent gate circuits on a single chip

- basic gates and flip-flops.

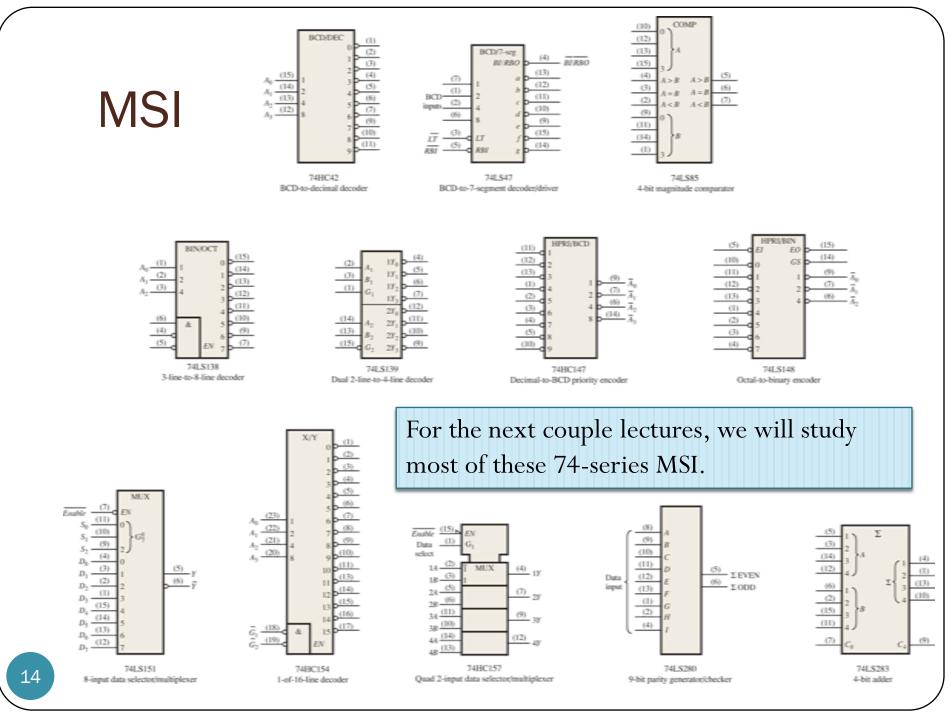

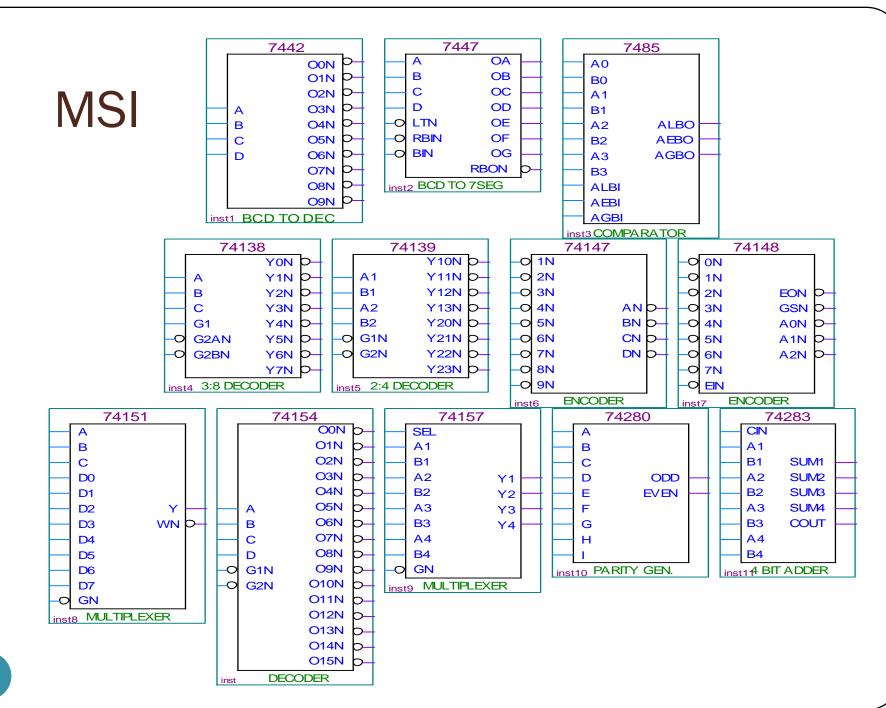

- Medium-scale integration (MSI)

- from 10 to 100 equivalent gates on a chip.

- encoders, decoders, counters, registers, multiplexers, arithmetic circuits, small memories

- Large-scale integration (LSI)

- Very large-scale integration (VLSI)

- Ultra large-scale integration (ULSI)

## SSI

5

'27

6 7

GND

2 3 4

2 3

1

5

6 7

GND

4

'30

4 5

'32

3

7

GND

6

7

GND

3 4

5 6

'86

2

## Simple Decoder

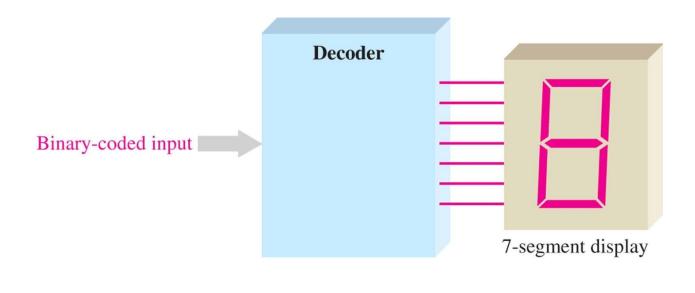

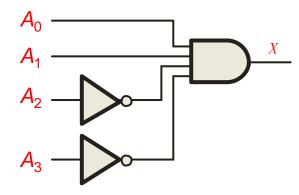

A **decoder** is a logic circuit that detects the presence of a specific combination of bits at its input.

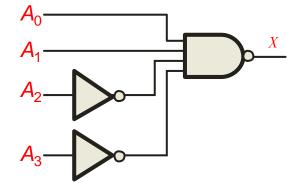

Two simple decoders that **detect the presence** of the binary code 0011 are shown below. The first has an active HIGH output; the second has an active LOW output.

Active HIGH decoder for 0011

Active LOW decoder for 0011

( $A_0$  is the LSB and  $A_3$  is the MSB)

## Exercise

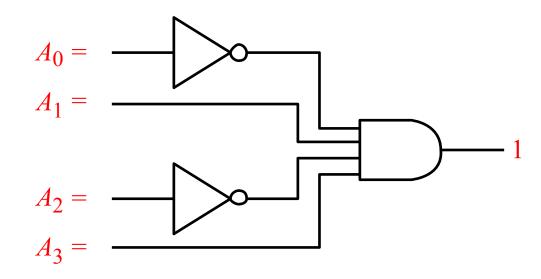

Assume the output of the decoder shown below is a logic 1. What are the inputs to the decoder?

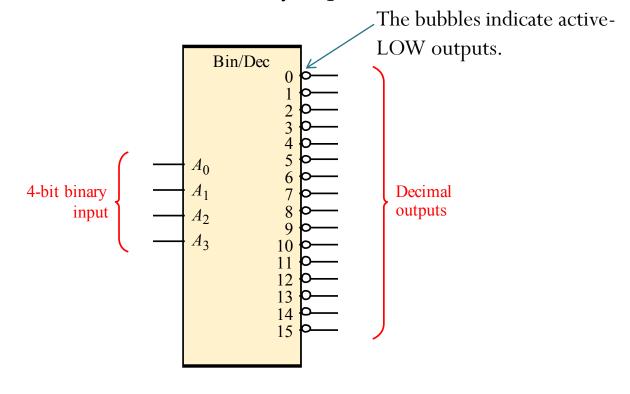

## **Binary-to-Decimal Decoder**

The binary-to-decimal decoder shown here has 16 outputs – one for each combination of binary inputs.

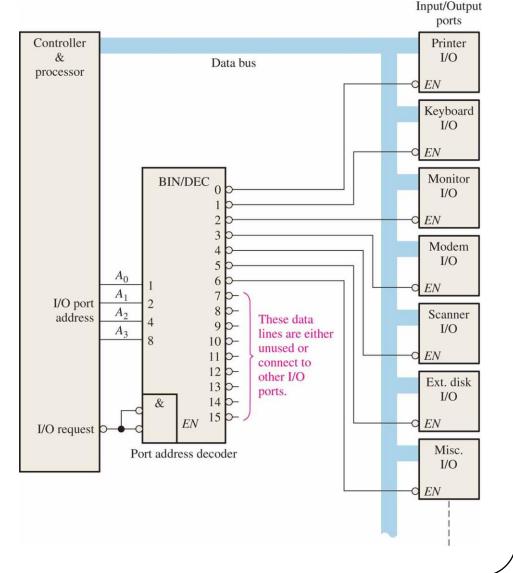

## Application: Port Address Decoder

- Decoder can be used in computers for input/output selection.

- Computers communicate with peripherals by sending and/or receiving data through what is known as input/output (I/O) ports.

- A decoder can be used to select the I/O port so that data can be sent or received from a specific external device.

## 2:4 decoder

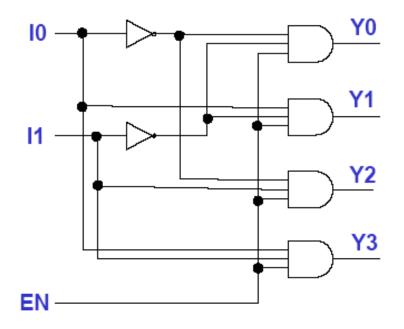

#### 2-to-4 line decoder with enable input

| lr | nput | s  | Outputs |   |   |   |  |  |

|----|------|----|---------|---|---|---|--|--|

| Ε  | 11   | 10 | Υ       | Υ | Υ | Υ |  |  |

| Ν  |      | 10 | 3       | 2 | 1 | 0 |  |  |

| 0  | X    | X  | 0       | 0 | 0 | 0 |  |  |

| 1  | 0    | 0  | 0       | 0 | 0 | 1 |  |  |

| 1  | 0    | 1  | 0       | 0 | 1 | 0 |  |  |

| 1  | 1    | 0  | 0       | 1 | 0 | 0 |  |  |

| 1  | 1    | 1  | 1       | 0 | 0 | 0 |  |  |

## Exercise

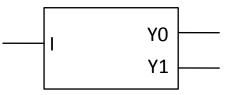

#### Find the truth table of the 1-to-2 line decoder below.

Then, implement the 1-to-2 line decoder.

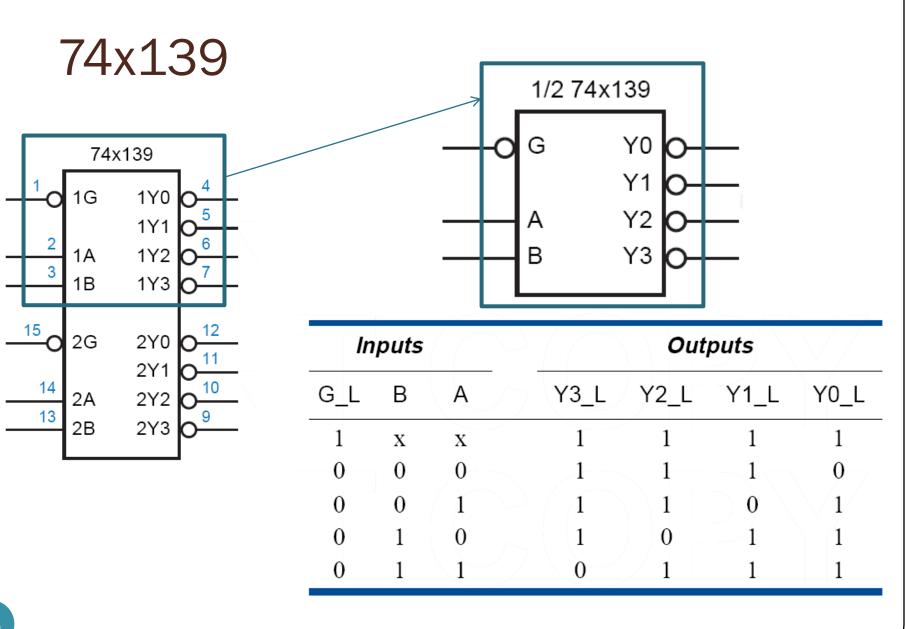

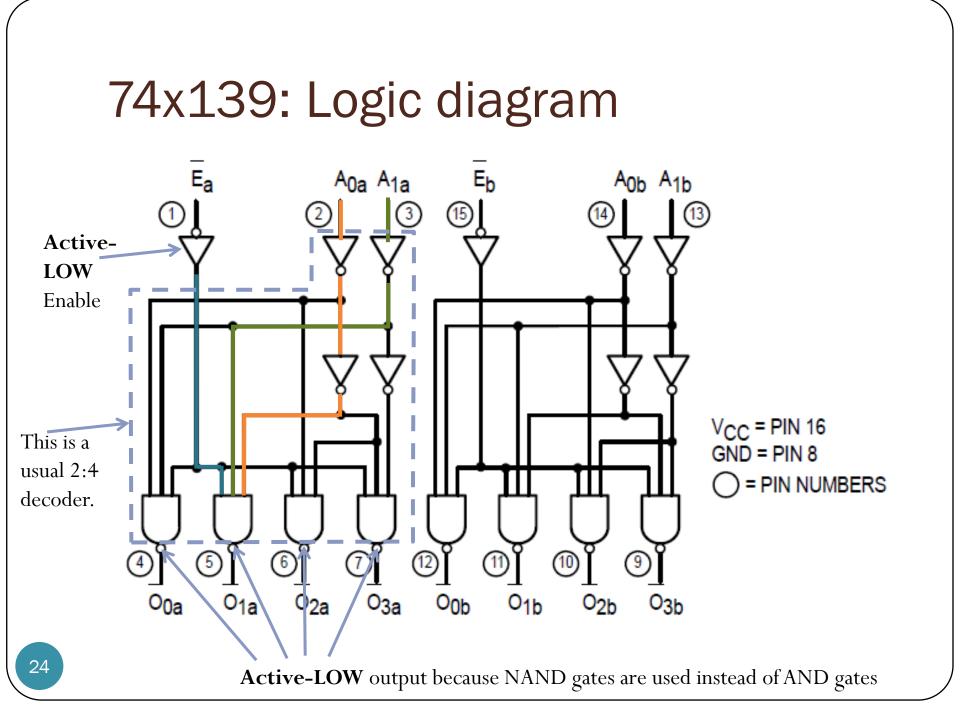

## 74x139: Dual 2:4 Decoder

Most MSI decoders were originally designed with active-LOW output.

- Two independent 2:4 decoders

- The outputs and the enable (E) input are active-LOW.

- When *E* is HIGH all outputs are forced HIGH.

V<sub>CC</sub> = PIN 16 GND = PIN 8

|   | INPUTS         | 5                             | OUTPUTS |                               |   |    |  |  |  |

|---|----------------|-------------------------------|---------|-------------------------------|---|----|--|--|--|

| E | A <sub>0</sub> | A <sub>0</sub> A <sub>1</sub> |         | 0 <sub>0</sub> 0 <sub>1</sub> |   | 03 |  |  |  |

| Н | Х              | Х                             | Н       | Н                             | Н | Н  |  |  |  |

| L | L              | L                             | L       | Н                             | Н | Н  |  |  |  |

| L | Н              | L                             | н       | L                             | Н | Н  |  |  |  |

| L | L              | Н                             | н       | Н                             | L | Н  |  |  |  |

| L | Н              | Н                             | н       | Н                             | Н | L  |  |  |  |

Notice that all of the signal names inside the symbol outline are active-HIGH, and that bubbles indicate active-LOW inputs and outputs.

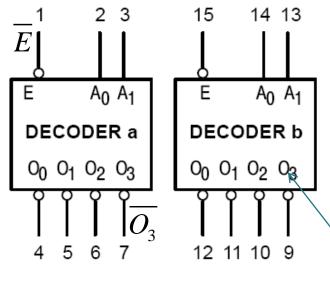

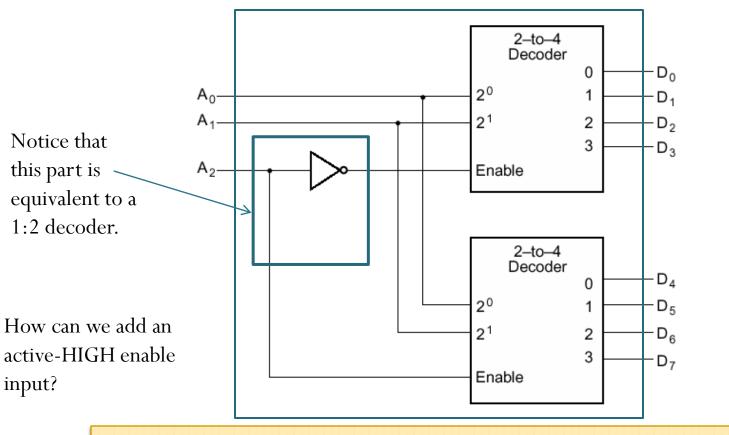

## Example: Building a larger decoder

Construct a 3-to-8 decoder from two 2-to-4 decoders

Low order bits  $(A_1, A_0)$  select within decoders. High order bit  $(A_2)$  controls which decoder is active.

25

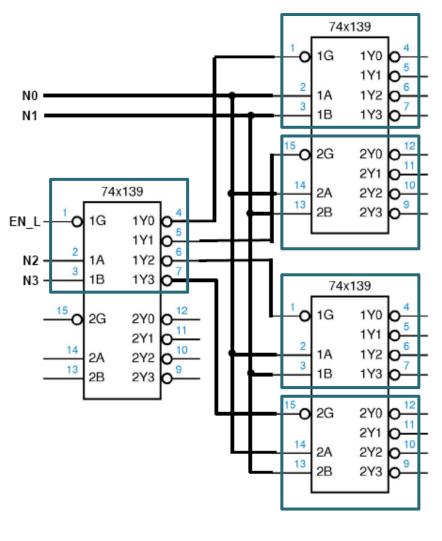

# Building larger decoder from smaller ones

- To construct (k+n)-to- $2^{n+k}$  decoders, can use

- 1.  $2^n$  of *k*-to- $2^k$  decoders with enable input and

- 2. one *n*-to-2*n* decoders.

- The connections are:

- For each of the k-to- $2^k$  decoder with enable input,

- all have k input

- we put in  $A_0 \dots A_{k-1}$ .

- The enable line of the  $r^{\text{th}}$  decoder is connected to  $D_r$  of the *n*-to- $2^n$  decoders.

- The inputs of the *n*-to- $2^n$  decoder get  $A_k$  to  $A_{n+k-1}$ .

- Basically, each k-to- $2^k$  decoder works on the last k bits.

- We use the first *n* bit, via the *n*-to-2<sup>*n*</sup> decoder, to select which one (and only one) of the *k*-to-2<sup>*k*</sup> decoders will be enabled.

## Example

Construct a 4:16 decoder with an active-LOW enable from three 2:4 decoders.

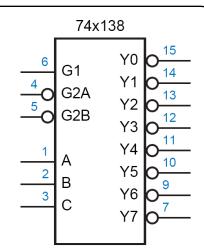

## 74x138: 3:8 Decoder

- Active-LOW outputs

- Three enable inputs.

| Inputs |       |       |   |   | Outputs |      |      |      |      |      |      |      |      |

|--------|-------|-------|---|---|---------|------|------|------|------|------|------|------|------|

| G1     | G2A_L | G2B_L | С | В | А       | Y7_L | Y6_L | Y5_L | Y4_L | Y3_L | Y2_L | Y1_L | Y0_L |

| 0      | x     | х     | х | x | x       | 1    | 1    | 1    | 1    | 1    | 1    | 1    | /1   |

| x      | 1     | х     | х | x | x       | 1    | 1    | 1    | _1   | 1    | 1    | 1    | 1    |

| x      | x     | 1     | х | x | x       | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| 1      | 0     | 0     | 0 | 0 | 0       | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    |

| 1      | 0     | 0     | 0 | 0 | 1       | 1    | 1    | 1    | 1    | 1    | 1    | 0    | /1   |

| 1      | 0     | 0     | 0 | 1 | 0       | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1    |

| 1      | 0     | 0     | 0 | 1 | 1       | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 1    |

| 1      | 0     | 0     | 1 | 0 | 0       | 1    | 1    | 1    | 0    | 1    | 1    | 1    | / 1/ |

| 1      | 0     | 0     | 1 | 0 | 1       | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 1    |

| 1      | 0     | 0     | 1 | 1 | 0       | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1    |

| 1      | 0     | 0     | 1 | 1 | 1       | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

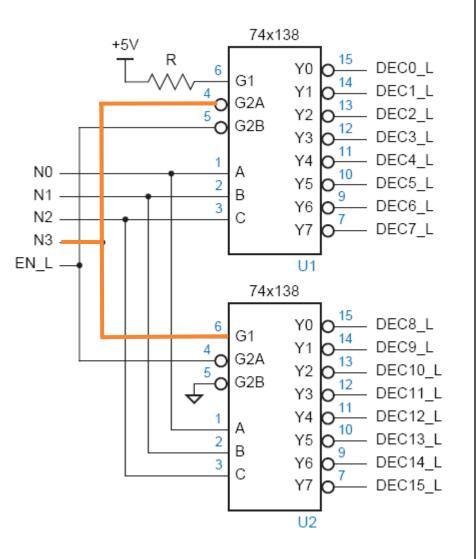

## Example

Construct a 4:16 decoder with an active-LOW enable (EN) from two 74x138 decoder.

**O11N**

**O12N**

**O13N**

**O14N**

015N

DECODER

inst

D-

D

n

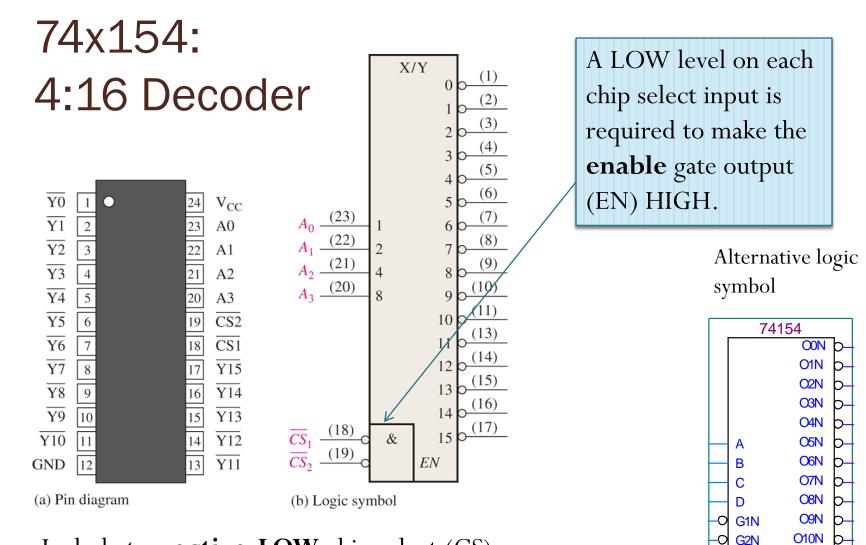

b

Include two **active-LOW** chip select (CS) lines which must be at the active level to enable the outputs. These lines can be used to expand the decoder to larger inputs.

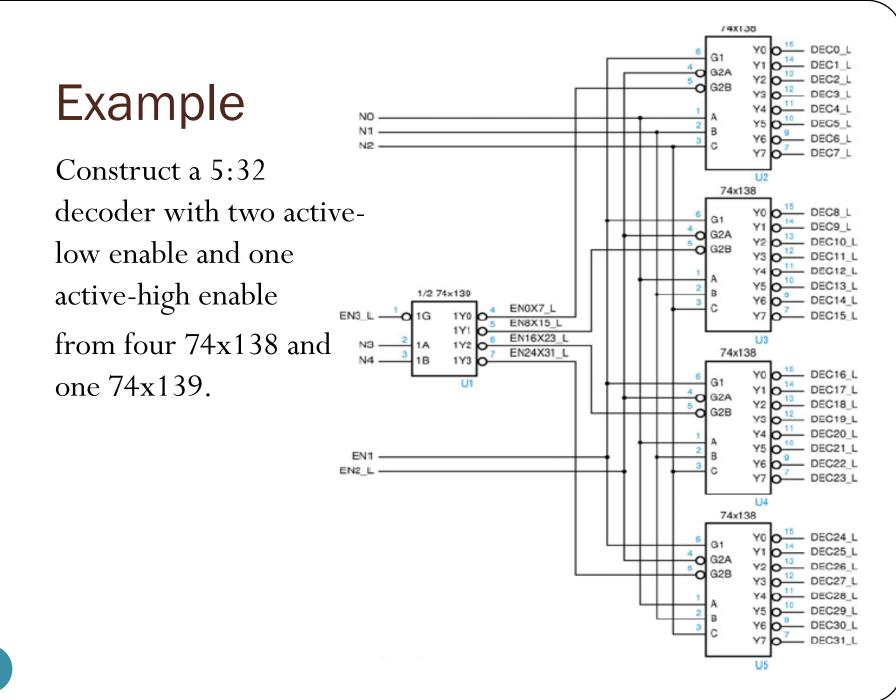

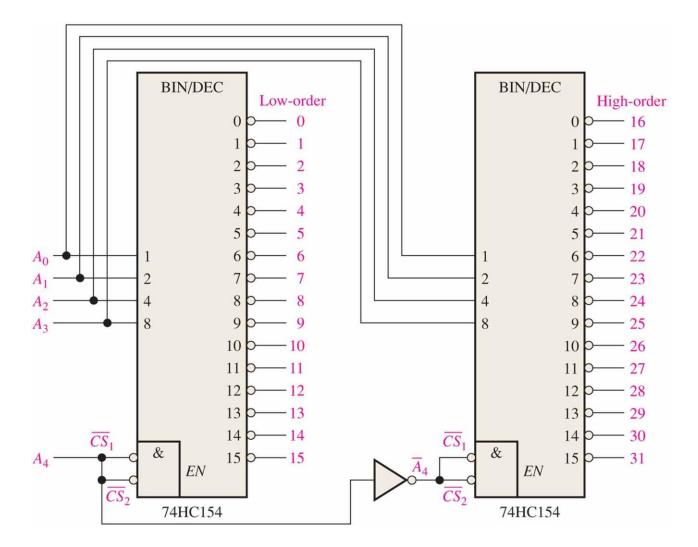

## 5:32 Decoder

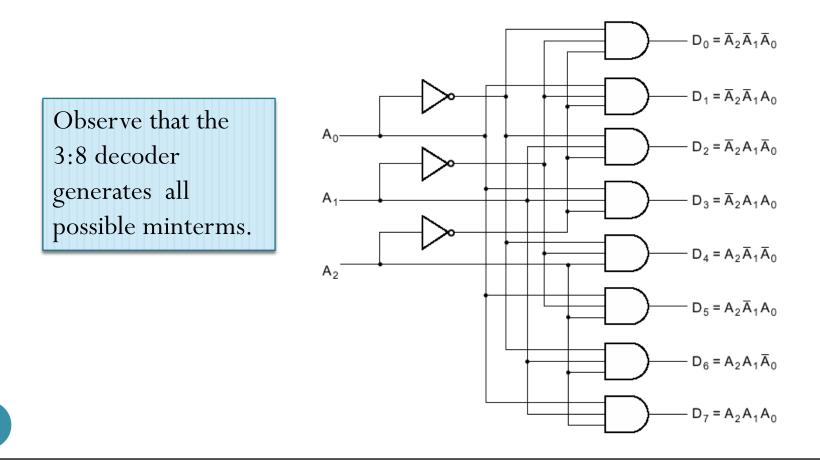

## Decoder as general purpose logic

Any combinational circuit with *n* inputs and *m* outputs can be implemented with an *n*-to- $2^n$ -line decoder and *m* OR gate

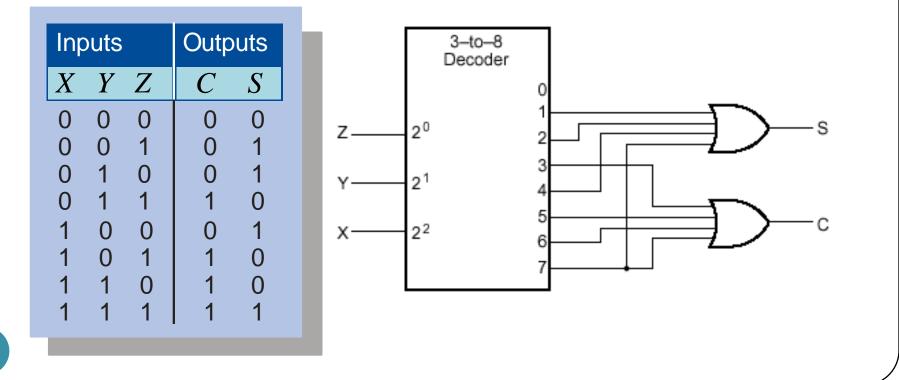

## Example

Implement a full adder circuit with a decoder and OR gates

•

$$S = \sum_{X,Y,Z} (1,2,4,7)$$

•

$$C = \sum_{X,Y,Z} (3,5,6,7)$$

## **Other Decoders**

In general, a decoder converts coded information, such as binary number, into non-coded form.

Later, (if time permitted) we will talk about other types of decoder.